ASMedia Preps USB4 v2 Controller and PHY

by Anton Shilov on June 12, 2024 8:00 AM EST- Posted in

- Peripherals

- Trade Shows

- ASMedia

- USB4

- USB4 v2

- Computex 2024

The USB Implementers Forum (USB-IF) introduced USB4 version 2.0 in fall 2022, and it expects systems and devices with the tech to emerge later this year and into next year. These upcoming products will largely rely on Intel's Barlow Ridge controller, a full-featured Thunderbolt 5 controller that goes above and beond the baseline USB4 v2 spec. And though extremely capable, Intel's Thunderbolt controllers are also quite expensive, and Barlow Ridge isn't expected to be any different. Fortunately, for system and device vendors that just need a basic USB4 v2 solution, ASMedia is also working on its own USB4 v2 controller.

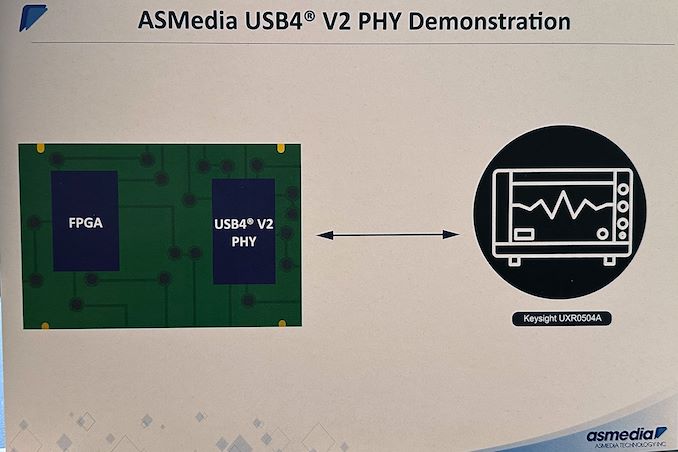

At Computex 2024, ASMedia demonstrated a prototype of its upcoming USB4 v2 physical interface (PHY), which will support USB4 v2's new Gen 4 (160Gbps) data rates and the associated PAM-3 signal encoding. The prototype was implemented using an FPGA, as the company yet has to tape out the completed controller.

Ultimately, the purpose of showing off a FPGA-based PHY at Computex was to allow ASMedia to demonstrate their current PHY design. With the shift to PAM-3 encoding for USB4 v2, ASMedia (and the rest of the USB ecosystem) must develop significantly more complex controllers – and there's no part of that more critical than a solid and reliable PHY design.

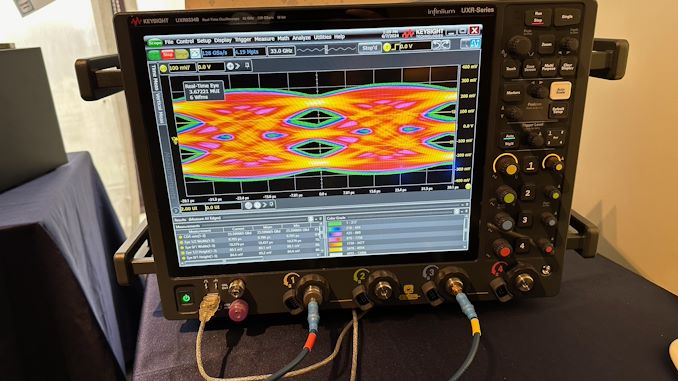

As part of their demonstration, ASMedia had a classic eye diagram display. The eye diagram demoed has a clear opening in the center, which is indicative of good signal integrity, as the larger the eye opening, the less distortion and noise in the signal. The horizontal width of the eye opening represents the time window in which the signal can be sampled correctly, so the relatively narrow horizontal spread of the eye opening suggests that there is minimal jitter, meaning the signal transitions are consistent and predictable. Finally, the vertical height of the eye opening indicates the signal amplitude and the rather tall eye opening suggests a higher signal-to-noise ratio (SNR), meaning that the signal is strong compared to any noise present.

ASMedia itself is one of the major suppliers for discrete USB controllers, so the availability of ASMedia's USB4 v2 chip is crucial for adoption of the standard in general. While Intel will spearhead the industry with their Barlow Ridge Thunderbolt 5/USB4 v2 controller, ASMedia's controller is poised to end up in a far larger range of devices. So the importance of the company's USB4 v2 PHY demo is hard to overstate.

Demos aside, ASMedia is hoping to tape the chip out soon. If all goes well, the company expects their first USB4 v2 controllers to hit the market some time in the second half of 2025.

Source: ASMedia

8 Comments

View All Comments

ballsystemlord - Wednesday, June 12, 2024 - link

That is one powerful oscilloscope. 33Ghz!The ASMedia USB controller is cool too, of course.

juancn - Wednesday, July 3, 2024 - link

Talk about a flex! Those go for 250k and above.dwillmore - Wednesday, June 12, 2024 - link

I take issue with using an FPGA to demonstrate a PHY. A phy is a digital to analog (and the reverse) type of device. The FPGA is just a digital device. If it has some kind of D/A in it, then this is more a demonstration of the FPGAs PHY abilities. So looking at they eye diagram tells us little about the Asmedia design. (Okay, if clocked poorly by their digital design, the horizintal width of the eye can be lower due to increased jitter), but the vertical SNR aspect of it will not be effected as that's a pure analog part of the design.The take away is that this demonstration--if it is as has been described--is pretty meaningless.

Also, thank you for explaining to people how to read an eye diagram. Very few people--even those in the industry--know how to read one. Good job!

The Von Matrices - Wednesday, June 12, 2024 - link

I am surprised about the use of an FPGA primarily because I did not know that any FPGA had SerDes hardware that could operate at these speeds.erinadreno - Friday, June 14, 2024 - link

The FPGA certainly has SerDes hardware capable of 100Gbps per lane with multiple lanes per device. But I suspect they aren't using those SerDes transceivers directly as no FPGA supports PAM3.It's easier to design a PAM3 SerDes PHY than the complete controller that has to account for power management, link negotiation, maybe tunneling, etc.

Kevin G - Wednesday, June 12, 2024 - link

With PAM3, you should have two eye openings which is shown in the picture. PAM4 would have three eye openings. The number of openings is tied to the number of possible state transitions possible in the system. For PAM3, you have + to -, + to 0, - to 0 and then those again in the opposite direction.Not to undermine Asmedia's here at getting 40 Gbit rates over a single lane (the 160 Gbit transfer figures is across four lanes for reference) is still an accomplishment. However, the image isn't perfect as the two eyes are not perfectly aligned nor symmetrical which would indicate a cleaner signal. What they have presented should work fine but more of a nitpick that this is not a textbook perfect signal example.

The Von Matrices - Wednesday, June 12, 2024 - link

The article says "the relatively narrow horizontal spread of the eye opening suggests that there is minimal jitter, meaning the signal transitions are consistent and predictable"Shouldn't wider horizontal openings represent less jitter?

PeachNCream - Wednesday, June 12, 2024 - link

It's nice to see USB Next, but like any first generation hardware, few if any people are going to care much until it's integrated and just ships as a mundane feature that doesn't demand an AIB or kludge-fest primitive mess to just work and for USB4, that'll be a while.