TSMC Teases 12-High 3D Stacked Silicon: SoIC Goes Extreme

by Dr. Ian Cutress on August 25, 2020 1:00 PM EST- Posted in

- CPUs

- GPUs

- TSMC

- CoWoS

- TSMC Tech Day 2020

I’ve maintained for a couple of years now that the future battleground when it comes to next-generation silicon is going to be in the interconnect – implicitly this relies on a very strong catalogue of advanced packaging techniques in order to apply those interconnects and bring chips together. As we bring those chips closer together, elements such as power, thermals, and design complexity all get thrown into the mix, and it makes it very difficult to produce multi-connected products at high yield, moreso if they are stacked vertically rather than horizontally. This is why what TSMC showed at its Technology Symposium this week all the more crazy.

For some background, one set of technologies that TSMC has in its hand is SoIC: System on Integrated Chip. This is a key future TSMC integration technology that goes beyond past interposer or chip-stacking implementations, in that it allows stacking of silicon dies without the use of any µ-bumps at all, instead aligning and bonding the metal layers of the silicon directly to each other.

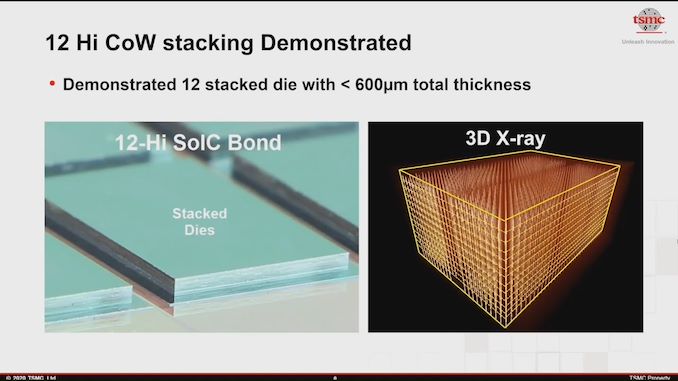

A single slide at the Technology Symposium shows it all off. TMSC is currently probing 12-Hi configurations of SoIC. Each of the dies within the 12-Hi stack has a series of through silicon vias (TSVs) in order for each layer to communicate with the rest of the layers, and the idea is that each layer could be a different element of logic, of IO, of SRAM, or could be passive to act as a thermal insulation layer between other active layers.

This design, as shown in the slide, has a maximum 600 micron thickness according to TSMC, which means that each layer is in the sub-50 micron level. Note that the bump pitch on a standard traditional die-stacking solution can be of the order of 50 microns. In the case of SoIC, the hybrid-bonding pitch is on the scale of 9µm for N7/N6 chips and 6µm for N5 chips. It shows that TSMC has some impressive linear manufacturing and wafer thinning technologies at hand in order to get this level of consistency and aligning of dies. The company has even demonstrated the capability to reduce this down to 0.9µm, a scale at which it would allow it to extend the back-end-of-line interconnect of a silicon chip.

The test chip shown in the slide is likely to be, if it is to showcase some initial runs, only 12 layers of passive silicon with basic TSV management. Obviously building something like this, thermals are going to come into play, but the main aspect here from TSMC’s point of view is that they can build it. It’s now up to the customers to book their place in line for the technology.

Carousel Image from Taiwan Semiconductor Manufacturing Co., Ltd.

Related Reading

- TSMC Details 3nm Process Technology: Full Node Scaling for 2H22 Volume Production

- TSMC To Build 5nm Fab In Arizona, Set To Come Online In 2024

- TSMC & Broadcom Develop 1,700 mm2 CoWoS Interposer: 2X Larger Than Reticles

- TSMC Boosts CapEx by $1 Billion, Expects N5 Node to Be Major Success

- Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

- TSMC: 5nm on Track for Q2 2020 HVM, Will Ramp Faster Than 7nm

- TSMC: N7+ EUV Process Technology in High Volume, 6nm (N6) Coming Soon

15 Comments

View All Comments

psychobriggsy - Tuesday, August 25, 2020 - link

Can you imagine: 1 layer of CPU cores, 1 layer 'passive heatspreader silicon', 8 layers of SRAM, 1 layer of I/O and another passive layer.Or 4 layers of slower CPU/GPU cores and 8 layers of SRAM.

64C Threadripper in a single stack with 512MB L3 cache...

Valantar - Tuesday, August 25, 2020 - link

... and a smoldering hole in your motherboard within seconds of powering on, I assume?On a more serious note, this sounds like it would have serious potential for shrinking SoCs in a dramatic way, but power and heat density would be an issue. It would also be interesting if TSMC were to cooperate with a memory manufacturer to get HBM into a setup like this. An 8-high stack of HBM + the active die at the base of the stack would leave three layers for something like a GPU. Or two stacks next to each other if you need more area for the GPU, of course. Could stick the less hot running parts like encode/decode on a layer below the main GPU layer.

name99 - Wednesday, August 26, 2020 - link

Amazing.EVERY time 3D stacking is mentioned, we get the people telling us it won't work because of heat issues. Poor TSMC -- they spent billions developing this tech, but nobody in the company was smart enough to validate whether there were any use cases that won't be thermally overloaded.

Oh well, that's what happens when you don't use random internet commenters to head your product strategy.

brunis.dk - Friday, August 28, 2020 - link

Local warming is real! :Dsaratoga4 - Sunday, August 30, 2020 - link

Stacking for low power SOCs makes a lot of sense, but the OP's idea of a 64 core Zen processor under 8-12 layers is absolutely not going to happen for thermal reasons.quadibloc - Tuesday, October 26, 2021 - link

Well, it is obvious it won't work for the kinds of things that would be really exciting. But, yes, obviously it will work for stuff like DRAM.astroboy888 - Thursday, August 27, 2020 - link

A 2009 3DIC study done by Stanford comparing 3D stacked memory vs. traditional 2D connected memory founds that power dissipation can be reduced by as much as 5X in a 3D stacked configuration.https://isl.stanford.edu/people/abbas/papers/conf%...

Rudde - Wednesday, August 26, 2020 - link

Having the cores on their own chiplets have its own advantages. It also keeps the power consumption down per stack. 512MB L3 cache for say 16 cores would be crazy amounts when scaled to 256 cores (16 chiplets) and beyond. The IO might also have its own stack allowing it to have larger/additional memory/pcie controllers.Why scale either out or up? Why not both?

MrEcho - Tuesday, August 25, 2020 - link

It will be interesting to see how they deal with heat with so many layers. Maybe its only 2 layers of transistors, with all the interconnect logic between them. Transistor sandwich if you will :)brucethemoose - Tuesday, August 25, 2020 - link

Amazing! I can't even imagine the kind of precision they need to line everything up.I wonder how many layers they can eventually do? If they could stick enough system memory right below the compute dies, it would turn modern processor design on its head.