Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

by Anton Shilov on October 4, 2019 1:00 PM EST- Posted in

- Interconnect

- Memory

- Enterprise

- Fabric

- Gen-Z

- PCIe

- PCIe 5.0

The Gen-Z Consortium this week released Physical Layer Specification 1.1 for Gen-Z interconnects. The new standard adds enhanced support for PCIe Gen 5 as well as Gen-Z 50G Fabric and Local PHY. The publication of the new PHY revision enables chip developers to implement support for the technologies in upcoming devices featuring Gen-Z interconnects.

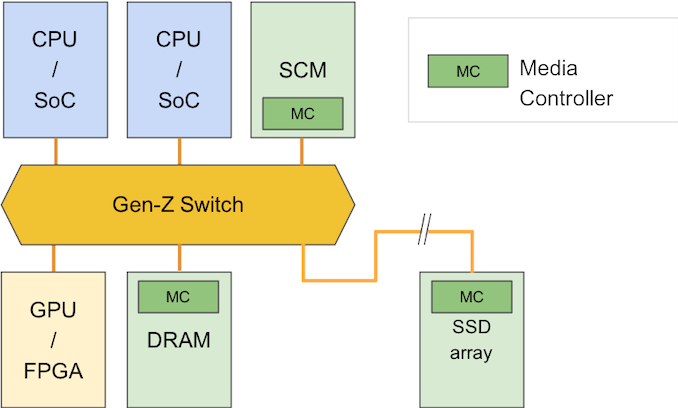

Designed to offer high bandwidth and low latency for connections between processors, co-processors/accelerators, and memory/fast storage, Gen-Z 1.0 uses a PCIe physical layer and a modified IEEE 802.3 Ethernet electrical layer standards to provide per-lane speeds of up to the 56 GigaTransfers/second. The Gen-Z 1.0 physical layer specification only defined usage of PCIe Gen 1-4 protocols as well as a 25 GT/s PHY. Thus, to take advantage of all the capabilities of the Gen-Z 1.0 core specification, one needs to comply with the Gen-Z PHY that describes logical, functional, electrical, and channel characteristics for various PHY layers.

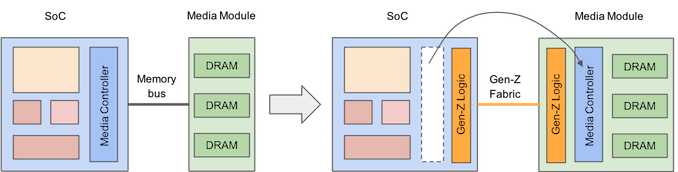

From CPU-memory interface to media-agnostic fabric

The Gen-Z Physical Layer Specification 1.1 defines how to implement a Gen-Z layer capable of operating at PCIe Gen 5 32 GT/s per lane speeds. Revision 1.1 also outlines how to implement a medium to reach a Gen-Z-E-PAM4-50G-Fabric link with a raw data rate of 53.125 GT/s per lane using a 4-level Pulse Amplitude Modulation (PAM4) signaling over the fabric with an ultra-low-latency Phit Forward Error Correction (Phit FEC) encoding using a BCH codeword. Finally, the specification 1.1 describes the implementation of a very short reach Gen-Z-E-PAM4-50G-Local link at 53.125 GT/s per lane using a PAM4 signaling with Forward Error Correction (raw data-rate of 47.222 GT/s).

System architecture with Gen-Z

In addition to the Physical Layer Specification 1.1, Gen-Z has eight more final specifications and five draft specifications available.

Related Reading

- Hot Chips 31 Live Blogs: Gen-Z Chipset for Exascale Fabric

- SMART Modular Shows Off 256 GB Gen-Z Memory Module

- Hot Chips 31 (2019) Programme Announced: Zen, Navi, POWER, Lakefield, Gen-Z, Turing, Lisa Su Keynote

- Gen-Z Interconnect Core Specification 1.0 Published

- Gen-Z Consortium Formed: Developing a New Memory Interconnect

Source: Gen-Z Consortium

Image Source: PLDA

8 Comments

View All Comments

twotwotwo - Friday, October 4, 2019 - link

PAM4 + forward error correction also sounds a lot like PCIe 6. Anyone know if the GenZ spec references PCIe 6 here, or have they forked/copied the early work on PCIe 6 (maybe so they can publish a spec before PCIe 6 is locked down), or is this two parallel efforts converging on similar approaches?jeremyshaw - Friday, October 4, 2019 - link

As long as we don't end up with a RAMBUS situation. In that case, I am hoping for the latter.Santoval - Friday, October 4, 2019 - link

PAM4 is also used for Ethernet, it's not exactly a brand new modulation technique. I don't think this is related in any way to PCIe 6.0. GenZ will surely employ PCIe 6.0 when it is finalized, but currently its 1.1. revision is based on PCIe 5.0Santoval - Saturday, October 5, 2019 - link

Since the "media controllers" in the pictures includes memory controllers (beside SSD controllers) I guess this means that GenZ moves the memory controller from the SoC/CPU to the DRAM modules. The first picture clearly shows that move.How would that work exactly? Wouldn't both SoC/CPU and DRAM vendors need to co-operate? Would they? Is this part of the push for "in-memory computing", where a "smart" controller with some extra computing functions for simple but frequent tasks moves very close to (or even *in*) the memory to alleviate the system memory - CPU bottleneck?

I believe a while ago a memory module was reported here that had quite a few basic logic blocks inside every DRAM die. I cannot recall if that module was designed for GenZ though. I think it was.

levizx - Saturday, October 5, 2019 - link

Think Ryzen I/O dieDiogene7 - Saturday, October 5, 2019 - link

@Anton Shilov: My understanding is that as of 2018 / 2019, the focus of the Gen-z protocol is more for data-centers applications.But I was wondering in approx what timeframe we might see an evolution of the specification for mobile SoC / laptop computers ?

I do really believe that such architecture would open new exciting innovation opportunities for those devices by, finally, having for example Storage Class Memory (SCM) (ex: MRAM, Carbon Nanotubes RAM (NRAM),...) integrated in smartphone / laptops : it would tremendously reduce data access latency and I am looking forward to this happening : the sooner, the better !!!

I looking for an idea of an approx. timeframe (ex : 2022 / 2025)...

I believe it would improve the overall user experience in a similar (and actually even more) way as flash SSD did when replacing HDD in laptops...

thomasg - Sunday, October 6, 2019 - link

I don't see that happening for some time, for a multitude of reasons.First, SCMs simply don't exist yet. Yes, 3D X-Point exists, but it just isn't what was promised, and maybe won't be for years to come. The rest is even further in the future.

When they exist, they need to become affordable; and even more, they need to be efficient, which seems quite unlikely.

Certainly, SCMs will not exist by 2022 and likely not by 2025, and surely won't be available in phones by 2025.

There's a reason we don't see PCIe used at all by phones.

Gen-Z isn't available yet in any form and it will clearly be much more expensive than PCIe and use far more power due to its complex nature.

I wouldn't expect the first Gen-Z devices - in expensive server-type machines - before 2022.

It might be deployed in a modern supercomputer-design by 2024.

Just as a reminder: The PCIe 4.0 spec-preview was published in 2011, and early deployments happened in 2016. The PCIe people are a conservative bunch and final specs are released when hardware can be built.

The Gen-Z pre-spec (they call it 1.0) was released last year and adds several layers of complexity to PCIe (on the specification of which it heavily depends).

I would expect Gen-Z to trail PCIe for years to come, and when PCIe 5.0 devices become available, we have a timeline to when Gen-Z 1.1 devices will become available (will we ever see Gen-Z 1.0?).

Luffy1piece - Monday, October 7, 2019 - link

I've been looking forward to NVRAM(PCM, MRAM, NRAM, etc.) too, because that will be an actual major performance upgrade in almost a decade of laptop computing. Gen-Z does look like a solution to faster adoption of NVRAM but I don't think that will happen for laptops coz Intel - which has 85+% of laptop CPU market share - seems to have a conflict of interest due of its own product line of 3DX point and CXL, and its business plans seem to indicate that the company wants to increase its share in the memory and interconnect domain.But on the bright side NVRAM is being added to the DDR5 JEDEC standard, and at least NRAM has plans of being a direct DDR5 physical replacement. Therefore that plus some software support can make it possible for it to be available in 2-3 years (this is my guess). As for mobile SoC, since there is more competition due to more SoC makers unlike the Intel monopoly in PC, we can expect a faster evolution.

As for the 5 year-ish timeframe, we can see 3D stacked SoC in laptops and mobile, i.e. layers of CPU, GPU, RAM, IO, etc. stacked on top of each other on a single die. In that case Gen-Z will only remain important for the commercial use like data centers.